Providing computing resources

1. ARUZ

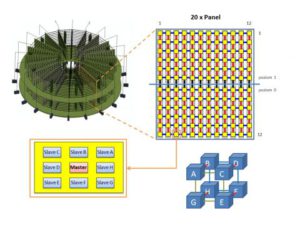

– 27 000 FPGA Artix 7 systems connected in a spatial network

– 75 000 connections

– 3 000 PCB boards

ARUZ (Real Complex Systems Analyzer) is a computational device based on FPGA integrated circuits. FPGAs are data processing units. However unlike for processors, their program is a network of logic gates rather than a list of commands to be executed.

ARUZ is of a cylindrical shape, 14 meters in diameter and 4.5 meters height. Computational circuits are placed on 20 vertical “walls” called panels. There are 150 printed circuit boards (PCB) on each panel arranged in 12.5 columns and 12 rows and 3000 computational boards in total. Besides that ARUZ is equipped with additional boards supporting communication and managing the device state. The boards are fixed to the water-cooled metal modules for heat dissipation.

All computational boards are connected forming a cubic lattice. 8 devices on each PCB are connected using printed circuits and devices placed on different (adjacent) PCBs are connected by twisted pair cables. Actual topology is a bit more complex than a simple cubic lattice. This allows for creation of a logical lattice with periodic boundary conditions without necessity of using long connection cables. Cables and connectors are standard LAN cables category 7. However the communication protocol is not Ethernet, it is a custom full-duplex protocol. All FPGA units use 125 MHz clock and data transmission modules: 500 MHz.

Original idea which stands behind ARUZ construction is electronic hardware implementation of DLL algorithm. DLL is a computational chemistry algorithm, which belongs to the Monte Carlo family and is a lattice simulation. It was developed in 1990’ by the late Prof. T. Pakuła. This algorithm is particularly useful for modelling properties of polymer solutions and gels and chemical reactions within them. We have also a unique opportunity to develop software for a lattice of 26 thousand connected powerful FPGA devises, which is, to our knowledge, the only one in the world.

- Jabłoński G., Kupis J.

2017 MIXDES – 24th International Conference ”Mixed Design of Integrated Circuits and Systems” (2017), pp. 308-313, 10.23919/MIXDES.2017.8005221 - Jabłoński G., Kupis J.

Int. J. Microelectron. Comput. Sci., 8 (1) (2017), pp. 36-42 - Jabłoński G., Kupis J.

2018 MIXDES – 25th International Conference ”Mixed Design of Integrated Circuits and Systems” (2018)

accepted for publication - Mudza Z., Kiełbik R., Rudnicki K., Amrozik., Jabłoński.:

ARUZ Dedicated Firmware, Book of Abstracts of ARUZ-Workshop 2016, pp. 45, Łódź, Poland, 1-3 December 2016, ISBN 978-83-7283-792-9 (poster) - KIEŁBIK R., JABŁOŃSKI G., AMROZIK P., MUDZA Z., KUPIS J.:

ARUZ – the unique massively parallel FPGA-based system, Book of Abstracts of ARUZ-Workshop 2016, pp. 8-9, Łódź, Poland, 1-3 December 2016, ISBN 978-83-7283-792-9

- Diffusion of small particles in polymer films (2017)

- Diffusive properties of solvent molecules in the neighborhood of a polymer chain as seen by Monte-Carlo simulations (2016)

- K. Halagan, P. Polanowski „Kinetics of spinodal decomposition in the Ising model with dynamic lattice liquid (DLL) Dynamics”, J. Non-Cryst. Solids 355 (2009) 1318.

- H. Gao, P. Polanowski, K. Matyjaszewski „Gelation in Living Copolymerization of Monomer and Divinyl Cross-Linker: Comparison of ATRP Experiments with Monte Carlo Simulations”, Macromolecules 42(2009) 5925.

- P. Polanowski „Parallel simulation of random fractal growth using dynamic lattice liquid (DLL) model”, J. Non-Cryst. Solids 353 (2007) 4575

- P. Polanowski, Z. Koza „Reaction-diffusion fronts in systems with concentration-dependent diffusivities”, Phys. Rev. E 74 (2006) 036103.

- T. Pakula, J. Mol. Liq. 86 (2000) 109

- T. Pakula, J. Teichmann, Mater. Res. Soc. Symp. Proc. 455 (1997) 211

2. Computer cluster

– 14 units, 330 cores, 672 threads

– 2 processors Xeon E5-2670v3 per unit

– 64GB RAM, 2×1.2TB

– Gigabit LAN